Difference between revisions of "Logic Shrimp"

Jump to navigation

Jump to search

Uwe Hermann (talk | contribs) m |

|||

| Line 1: | Line 1: | ||

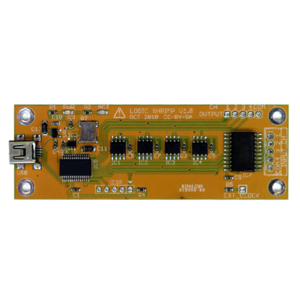

[[File:logic-shrimp-front.png|thumb|right|Logic Shrimp]] | [[File:logic-shrimp-front.png|thumb|right|Logic Shrimp]] | ||

[[File:logic-shrimp- | [[File:logic-shrimp-back.png|thumb|right|Back of PCB]] | ||

The [http://dangerousprototypes.com/docs/Logic_Shrimp_logic_analyzer Logic Shrimp] is a USB-based logic analyzer created by [http://dangerousprototypes.com/ Dangerous Prototypes]. The design is available under a Creative Commons (CC-BY-SA) license. | The [http://dangerousprototypes.com/docs/Logic_Shrimp_logic_analyzer Logic Shrimp] is a USB-based logic analyzer created by [http://dangerousprototypes.com/ Dangerous Prototypes]. The design is available under a Creative Commons (CC-BY-SA) license. | ||

Revision as of 22:06, 28 April 2011

The Logic Shrimp is a USB-based logic analyzer created by Dangerous Prototypes. The design is available under a Creative Commons (CC-BY-SA) license.

Hardware

The device essentially consists of a PIC microchip running at 20MHz, sampling each of its 4 probes into its own 256K SRAM chip. A buffer chip makes the design 5V tolerant.

Driver

The PIC uses the sump protocol, as used by the Openbench Logic Sniffer driver. It is thus supported in sigrok out of the box. However, the current firmware in the Logic Shrimp does not properly publish metadata according to its capabilities. In order to get valid data from it, make sure to always restrict the probes sampled to 1-4.