Difference between revisions of "Braintechnology USB Interface V2.x"

Jump to navigation

Jump to search

Uwe Hermann (talk | contribs) m |

|||

| (One intermediate revision by the same user not shown) | |||

| Line 1: | Line 1: | ||

[[File: | {{Infobox logic analyzer | ||

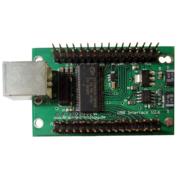

| image = [[File:Braintechnology_usb_interface_v26.png|180px]] | |||

| name = Braintechnology USB Interface V2.x | |||

| status = supported | |||

| source_code_dir = fx2lafw | |||

| channels = 8/16 | |||

| samplerate = 24MHz | |||

| samplerate_state = — | |||

| triggers = none (SW-only) | |||

| voltages = -0.5V — 5.25V | |||

| threshold = Fixed: VIH=2.0V—5.25V, VIL=-0.5V—0.8V | |||

| memory = none | |||

| compression = none | |||

| website = [http://www.braintechnology.de/braintechnology/en/usb_fastinterface27.html braintechnology.de] | |||

}} | |||

The | The '''Braintechnology USB Interface V2.x''' is a Cypress FX2 eval board, which can be used as USB-based, 16-channel logic analyzer with up to 24MHz sampling rate. | ||

There are various revisions of the hardware, e.g. [http://www.braintechnology.de/braintechnology/en/usb_fastinterface25.html V2.5], [http://www.braintechnology.de/braintechnology/en/usb_fastinterface26.html V2.6], and [http://www.braintechnology.de/braintechnology/en/usb_fastinterface27.html V2.7]. | There are various revisions of the hardware, e.g. [http://www.braintechnology.de/braintechnology/en/usb_fastinterface25.html V2.5], [http://www.braintechnology.de/braintechnology/en/usb_fastinterface26.html V2.6], and [http://www.braintechnology.de/braintechnology/en/usb_fastinterface27.html V2.7]. | ||

| Line 11: | Line 25: | ||

== Hardware == | == Hardware == | ||

* Main chip: Cypress CY7C68013A-56PVXC ( | * '''Main chip''': Cypress CY7C68013A-56PVXC (FX2LP) | ||

* 64kB I2C EEPROM: Microchip 24LC641 | * '''64kB I2C EEPROM''': Microchip 24LC641 | ||

* Low-dropout voltage regulator: ST LD33 | * '''Low-dropout voltage regulator''': ST LD33 | ||

* 24MHz | * '''Crystal''': 24MHz | ||

* PDEI | * '''?''': PDEI | ||

== Photos == | == Photos == | ||

| Line 22: | Line 36: | ||

File:Braintechnology usb interface v2x pcb front.jpg|<small>PCB, front</small> | File:Braintechnology usb interface v2x pcb front.jpg|<small>PCB, front</small> | ||

File:Braintechnology usb interface v2x pcb back.jpg|<small>PCB, back</small> | File:Braintechnology usb interface v2x pcb back.jpg|<small>PCB, back</small> | ||

File:Braintechnology usb interface v2x fx2.jpg|<small> | File:Braintechnology usb interface v2x fx2.jpg|<small>Cypress FX2LP</small> | ||

File:Braintechnology usb interface v2x eeprom ldo.jpg|<small>I2C EEPROM, LDO</small> | File:Braintechnology usb interface v2x eeprom ldo.jpg|<small>I2C EEPROM, LDO</small> | ||

File:Braintechnology usb interface v2x pdei.jpg|<small>PDEI chip</small> | File:Braintechnology usb interface v2x pdei.jpg|<small>PDEI chip</small> | ||

</gallery> | </gallery> | ||

== Protocol == | |||

Since we use the open-source [[fx2lafw]] firmware for this device, we don't need to know the protocol. | |||

== Resources == | |||

* [http://www.braintechnology.de/downstat18/download.php?file=schematicv27.pdf Schematics] | |||

* [http://www.braintechnology.de/braintechnology/en/usb_fastinterface27.html Various eval board documentation files] | |||

[[Category:Device]] | [[Category:Device]] | ||

[[Category:Logic analyzer]] | [[Category:Logic analyzer]] | ||

[[Category:Supported]] | [[Category:Supported]] | ||

Latest revision as of 11:08, 28 July 2013

| |

| Status | supported |

|---|---|

| Source code | fx2lafw |

| Channels | 8/16 |

| Samplerate | 24MHz |

| Samplerate (state) | — |

| Triggers | none (SW-only) |

| Min/max voltage | -0.5V — 5.25V |

| Threshold voltage | Fixed: VIH=2.0V—5.25V, VIL=-0.5V—0.8V |

| Memory | none |

| Compression | none |

| Website | braintechnology.de |

The Braintechnology USB Interface V2.x is a Cypress FX2 eval board, which can be used as USB-based, 16-channel logic analyzer with up to 24MHz sampling rate.

There are various revisions of the hardware, e.g. V2.5, V2.6, and V2.7.

In sigrok, we use the open-source fx2lafw firmware for this logic analyzer.

See Braintechnology USB Interface V2.x/Info for some more details (such as lsusb -vvv output) on the device.

Hardware

- Main chip: Cypress CY7C68013A-56PVXC (FX2LP)

- 64kB I2C EEPROM: Microchip 24LC641

- Low-dropout voltage regulator: ST LD33

- Crystal: 24MHz

- ?: PDEI

Photos

Protocol

Since we use the open-source fx2lafw firmware for this device, we don't need to know the protocol.