Difference between revisions of "Protocol decoder:Parallel"

Jump to navigation

Jump to search

Uwe Hermann (talk | contribs) m |

Uwe Hermann (talk | contribs) m |

||

| Line 11: | Line 11: | ||

| probes = — | | probes = — | ||

| optional_probes = CLK, D0-D63 | | optional_probes = CLK, D0-D63 | ||

| options = clock_edge, wordsize, endianness | |||

}} | }} | ||

The '''parallel''' protocol decoder can decode synchronous parallel buses with various number of data bits/probes and one clock line. | The '''parallel''' protocol decoder can decode (synchronous or asynchronous) parallel buses with various number of data bits/probes and one optional clock line. | ||

== Hardware == | == Hardware == | ||

There's a lot of hardware (ICs, connectors) that uses various kinds of sync or async parallel protocols. | |||

Generally there are a number of data lines (e.g. 8 or 16) and (in the synchronous case) a clock line. | |||

== Protocol == | == Protocol == | ||

On either the falling or rising clock edge one or more data lines (D0 up to possibly D63, for example) are sampled, and the individual probe values are combined to a number that is shown. | On either the falling or rising clock edge one or more data lines (D0 up to possibly D63, for example) are sampled, and the individual probe values are combined to a number that is shown. | ||

If no clock pin is supplied, the decoder works in asynchronous mode and samples the data lines upon each transition on any of the data lines. | |||

== Resources == | == Resources == | ||

Revision as of 00:10, 3 April 2015

| |

| Name | Parallel |

|---|---|

| Description | Generic parallel synchronous bus |

| Status | supported |

| License | GPLv2+ |

| Source code | decoders/parallel |

| Input | logic |

| Output | parallel |

| Probes | — |

| Optional probes | CLK, D0-D63 |

| Options | clock_edge, wordsize, endianness |

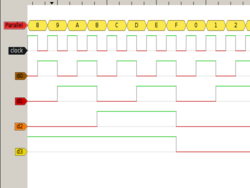

The parallel protocol decoder can decode (synchronous or asynchronous) parallel buses with various number of data bits/probes and one optional clock line.

Hardware

There's a lot of hardware (ICs, connectors) that uses various kinds of sync or async parallel protocols.

Generally there are a number of data lines (e.g. 8 or 16) and (in the synchronous case) a clock line.

Protocol

On either the falling or rising clock edge one or more data lines (D0 up to possibly D63, for example) are sampled, and the individual probe values are combined to a number that is shown.

If no clock pin is supplied, the decoder works in asynchronous mode and samples the data lines upon each transition on any of the data lines.