Difference between revisions of "HT USBee-AxPro"

Uwe Hermann (talk | contribs) |

m |

||

| Line 12: | Line 12: | ||

| memory = none | | memory = none | ||

| compression = none | | compression = none | ||

| price = $35 - $45 | |||

| website = [http://de.aliexpress.com/item/New-3-in-1-Tool-Oscilloscope-Logic-Analyzer-ALTERA-Saleae8-USBEE-AX-PRO-Altera-USB-Blaster/32236912930.html aliexpress.com] | | website = [http://de.aliexpress.com/item/New-3-in-1-Tool-Oscilloscope-Logic-Analyzer-ALTERA-Saleae8-USBEE-AX-PRO-Altera-USB-Blaster/32236912930.html aliexpress.com] | ||

}} | }} | ||

Latest revision as of 14:00, 30 June 2019

| |

| Status | supported |

|---|---|

| Source code | fx2lafw |

| Channels | 8 + 1 |

| Samplerate | 8ch @ 24MHz, 8+1ch @ 12MHz |

| Samplerate (state) | — |

| Triggers | none (SW-only) |

| Min/max voltage |

Digital: -1V — +6V Analog: ±10V (±20V max) |

| Threshold voltage | Fixed: VIH=1.6V, VIL=1.4V |

| Memory | none |

| Compression | none |

| Price range | $35 - $45 |

| Website | aliexpress.com |

The HT USBee-AxPro is a USB-based, 8-channel logic analyzer with up to 24MHz sampling rate, with 1 additional analog channel (3MHz analog bandwidth).

It is able to switch between USBee AX-Pro, Salea Logic and Altera USB blaster mode via a button. When pressing the button the USB VID/PID changes.

It is a clone of the CWAV USBee AX-Pro.

In sigrok, we use the open-source fx2lafw firmware for this logic analyzer.

See HT USBee-AxPro/Info for some more details (such as lsusb -v output) on the device.

Hardware

HT2013 V5.00:

- Main chip: Cypress CY7C68013A-56SSOP (FX2LP)

- 64Kbit I²C EEPROM: Microchip 24LC641

- 2Kbit I²C EEPROM: Microchip 24LC02B

- Auxiliary 8051 chip: ST STM8S003F3 (used for handling the button)

- Supply voltage regulator: Advanced Monolithic Systems AMS1117-3.3

- Analog-to-digital converter: Texas Instruments TLC5510I

- Analog input amplifiers: Analog Devices AD8065 (SMD marking "HRA")

- Analog amplifiers negative supply: Intersil ICL7660 (7660 AIBAZ V120428A)

- Crystal: 24MHz

FX2LP pin mappings

| # | Pin | Destination | Remark |

|---|---|---|---|

| CTL2 | ADC_CLK | ADC clock | |

| PD0..7 | ADC_D1..8 | ADC data output |

Analog frontend

Schematics:

Notes:

- Some devices have R2 = 66.5Ω (instead of 66.5kΩ), this basically limits the range to -3.3V — +3.3V.

- TLC5510 is used with ~3.3V "reference" from LDO output which is both out of the allowed range and is a major source of inaccuracy.

- Some devices (probably those that do not have U5 populated) produce bogus min and max spikes when measuring certain voltages, this can probably be remedied by adding small (on the order of 10s pF) capacitance to U5 Vcc and GND pins or to the ADC CLK line.

HT_V6.0:

- ...

Pin mappings

The FX2 CTL2 and PD0..7 pins are mapped exactly like the HT2013 V5.00 version. The TLC5510I OE# pin is tied to GND.

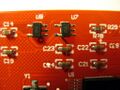

Photos

HT2013 V5.00:

HT2013 V5.00 (no blue button PCB):

HT_V6.0:

Protocol

Since we use the open-source fx2lafw firmware for this device, we don't need to know the protocol.