Difference between revisions of "DreamSourceLab DSLogic Basic"

Jump to navigation

Jump to search

Uwe Hermann (talk | contribs) (Created page with "{{Infobox logic analyzer | image = [[|180px]] | name = DreamSourceLab DSLogic Basic | status = supported | source_code_dir = dreamsourcelab-d...") |

Uwe Hermann (talk | contribs) |

||

| (6 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

{{Infobox logic analyzer | {{Infobox logic analyzer | ||

| image = [[180px]] | | image = [[File:DSLogic.png|180px]] | ||

| name = DreamSourceLab DSLogic Basic | | name = DreamSourceLab DSLogic Basic | ||

| status = supported | | status = supported | ||

| source_code_dir = dreamsourcelab-dslogic | | source_code_dir = dreamsourcelab-dslogic | ||

| channels = | | channels = 1-16 | ||

| samplerate = | | samplerate = 100MHz(3ch), 100MHz(6ch), 50MHz(9ch), 32MHz(12ch), 16MHz(16ch) | ||

| samplerate_state = | | samplerate_state = 30MHz (?) or 50MHz (?) | ||

| triggers = | | triggers = high, low, rising, falling, edge, multi-stage triggers | ||

| voltages = | | voltages = -0.6V — 6V | ||

| threshold = | | threshold = configurable: 0-5V (0.1V increments) | ||

| memory = | | memory = None | ||

| compression = yes | | compression = yes | ||

| website = [http://www.dreamsourcelab.com/dslogic.html dreamsourcelab.com] | | website = [http://www.dreamsourcelab.com/dslogic.html dreamsourcelab.com] | ||

| Line 20: | Line 20: | ||

== Hardware == | == Hardware == | ||

* '''FPGA''': Xilinx Spartan-6 XC6SLX9 | |||

* '''USB''': Cypress CY7C68013A (FX2) | |||

* '''I²C EEPROM''': ST 4128BRP | |||

* '''Crystal''': 24MHz | |||

== Photos == | == Photos == | ||

| Line 29: | Line 34: | ||

'''Cables''': | '''Cables''': | ||

<gallery> | <gallery> | ||

File:Dreamsourcelab dslogic basic cable 1.jpg | |||

File:Dreamsourcelab dslogic basic cable 2.jpg | |||

File:Dreamsourcelab dslogic basic cable 3.jpg | |||

File:Dreamsourcelab dslogic basic cable 4.jpg | |||

File:Dreamsourcelab dslogic basic cable 5.jpg | |||

File:Dreamsourcelab dslogic basic cable 6.jpg | |||

File:Dreamsourcelab dslogic basic cable 7.jpg | |||

File:Dreamsourcelab dslogic basic cable 8.jpg | |||

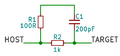

File:Dreamsourcelab dslogic basic probe circuit.png|<small>Probe cable circuit</small> | |||

</gallery> | </gallery> | ||

| Line 34: | Line 48: | ||

See [[DreamSourceLab DSLogic#Firmware]]. | See [[DreamSourceLab DSLogic#Firmware]]. | ||

'''Note''': The FX2 firmware is loaded at powerup from the I²C EEPROM on the PCB. | |||

=== EEPROM layout === | |||

The device has an I²C EEPROM with the following layout: | |||

<span style="background-color: orange">c2</span> <span style="background-color: lime">0e 2a</span> <span style="background-color: green">21 00</span> <span style="background-color: lightgreen">00 00</span> <span style="background-color: brown">04</span> <span style="background-color: yellow">XX XX XX XX XX XX .. ..</span> | |||

Description: | |||

{| border="0" style="font-size: smaller;" class="alternategrey sigroktable" | |||

!Bytes | |||

!Description | |||

|- | |||

| style="background-color: orange" | 0 | |||

| '''0xc2''': FX2 "c2 load" mode, i.e. VID/PID/DID are loaded from EEPROM as the firmware. | |||

|- | |||

| style="background-color: lime" | 1-2 | |||

| '''0x2a0e''': USB vendor ID (VID before firmware renumerate). | |||

|- | |||

| style="background-color: green" | 3-4 | |||

| '''0x0021''': USB product ID (PID before firmware renumerate). | |||

|- | |||

| style="background-color: lightgreen" | 5-6 | |||

| '''0x0000''': USB device ID (DID before firmware renumerate). | |||

|- | |||

| style="background-color: brown" | 7 | |||

| '''0x04''': FX2 configuration byte (see FX2 TRM for details). | |||

|- | |||

| style="background-color: yellow" | 8 - 6778 | |||

| Firmware (6771 bytes, sha1sum: 79784d038800e4b4757eba15de33813ac76819945f1b39239df6cf0a096dce55) | |||

|- | |||

| Rest | |||

| Unknown, probably all-0xff. | |||

|} | |||

== Resources == | == Resources == | ||

Latest revision as of 23:57, 15 April 2020

| |

| Status | supported |

|---|---|

| Source code | dreamsourcelab-dslogic |

| Channels | 1-16 |

| Samplerate | 100MHz(3ch), 100MHz(6ch), 50MHz(9ch), 32MHz(12ch), 16MHz(16ch) |

| Samplerate (state) | 30MHz (?) or 50MHz (?) |

| Triggers | high, low, rising, falling, edge, multi-stage triggers |

| Min/max voltage | -0.6V — 6V |

| Threshold voltage | configurable: 0-5V (0.1V increments) |

| Memory | None |

| Compression | yes |

| Website | dreamsourcelab.com |

The DreamSourceLab DSLogic Basic is a 16-channel USB-based logic analyzer, with sampling rates up to 400MHz (when using only 4 channels).

See DreamSourceLab DSLogic Basic/Info for more details (such as lsusb -v output) about the device.

Hardware

- FPGA: Xilinx Spartan-6 XC6SLX9

- USB: Cypress CY7C68013A (FX2)

- I²C EEPROM: ST 4128BRP

- Crystal: 24MHz

Photos

Device:

Cables:

Firmware

See DreamSourceLab DSLogic#Firmware.

Note: The FX2 firmware is loaded at powerup from the I²C EEPROM on the PCB.

EEPROM layout

The device has an I²C EEPROM with the following layout:

c2 0e 2a 21 00 00 00 04 XX XX XX XX XX XX .. ..

Description:

| Bytes | Description |

|---|---|

| 0 | 0xc2: FX2 "c2 load" mode, i.e. VID/PID/DID are loaded from EEPROM as the firmware. |

| 1-2 | 0x2a0e: USB vendor ID (VID before firmware renumerate). |

| 3-4 | 0x0021: USB product ID (PID before firmware renumerate). |

| 5-6 | 0x0000: USB device ID (DID before firmware renumerate). |

| 7 | 0x04: FX2 configuration byte (see FX2 TRM for details). |

| 8 - 6778 | Firmware (6771 bytes, sha1sum: 79784d038800e4b4757eba15de33813ac76819945f1b39239df6cf0a096dce55) |

| Rest | Unknown, probably all-0xff. |