Difference between revisions of "Sysclk LWLA1034"

Jump to navigation

Jump to search

(Begin documentation of reverse engineering effort) |

|||

| Line 24: | Line 24: | ||

[[File:Sysclk lwla1034 software.png]] | [[File:Sysclk lwla1034 software.png]] | ||

== | == Firmware == | ||

* The FX2 firmware appears to be loaded from an EEPROM on the board, so that the final USB device descriptor is immediately available on power-up. | |||

* End point 4 appears to be used exclusively for loading a new bitstream into the FPGA. | |||

* End point 2 is apparently used for sending commands to the FPGA firmware, with responses (if any) coming in from end point 6. | |||

Reverse engineering of the vendor protocol is currently in progress. See [[Sysclk LWLA1034/Protocol]] for a documentation of the findings gathered so far. | |||

== Resources == | == Resources == | ||

Revision as of 18:27, 21 December 2013

The Sysclk LWLA1034 is a USB-based, 34-channel logic analyzer with up to 125MHz sampling rate.

See Sysclk LWLA1034/Info for more details (such as lsusb -vvv output) about the device.

Hardware

- Altera Cyclone II FPGA

- Cypress CY7C68013A-56 (FX2) USB interface chip

- SRAM chip?

Photos

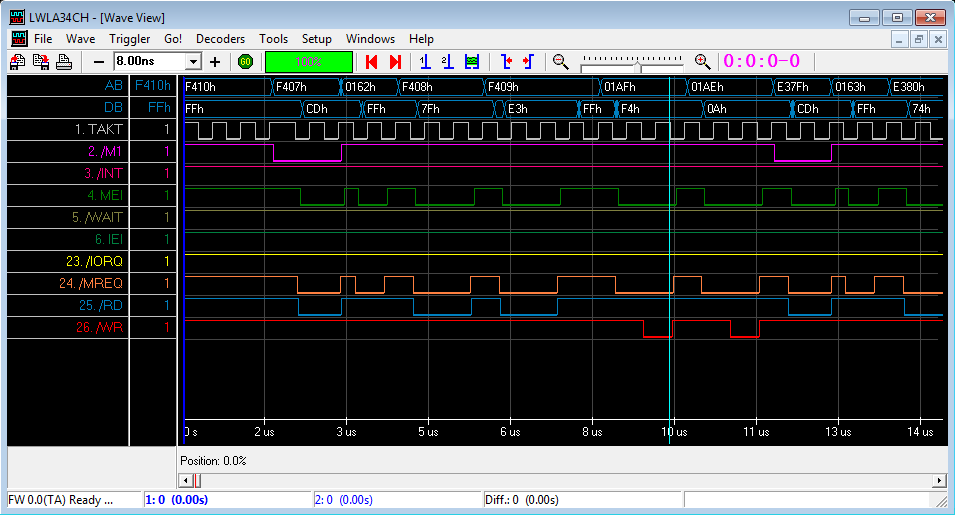

Software

Firmware

- The FX2 firmware appears to be loaded from an EEPROM on the board, so that the final USB device descriptor is immediately available on power-up.

- End point 4 appears to be used exclusively for loading a new bitstream into the FPGA.

- End point 2 is apparently used for sending commands to the FPGA firmware, with responses (if any) coming in from end point 6.

Reverse engineering of the vendor protocol is currently in progress. See Sysclk LWLA1034/Protocol for a documentation of the findings gathered so far.