Difference between revisions of "MiniLA"

Jump to navigation

Jump to search

Uwe Hermann (talk | contribs) (Created page with "{{Infobox logic analyzer | image = 180px | name = MiniLA | status = planned | source_code_dir = | channels ...") |

(No difference)

|

Revision as of 16:02, 8 June 2013

| |

| Status | planned |

|---|---|

| Channels | 32 |

| Samplerate | 100MHz |

| Samplerate (state) | ? |

| Triggers | low, high, rising, falling, don't care |

| Min/max voltage | ? |

| Threshold voltage | ? |

| Memory | 128Kb/channel |

| Compression | ? |

| Website | minila.sf.net |

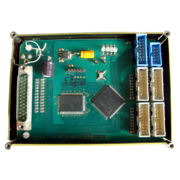

The MiniLA is a parallel port based, 32-channel logic analyzer with up to 100MHz sampling rate.

It is an open-hardware / open-source design.

Hardware

TODO.

Photos

TODO.

Protocol

TODO.