Difference between revisions of "Mcupro Logic16 clone"

m |

|||

| (9 intermediate revisions by 3 users not shown) | |||

| Line 13: | Line 13: | ||

| memory = none | | memory = none | ||

| compression = yes | | compression = yes | ||

| website = [ | | price = $30 - $35 | ||

| website = [https://www.aliexpress.com/item/new-USB-Logic-100MHz-16Ch-Logic-Analyzer-for-ARM-FPGA-E4-004/32931358747.html aliexpress.com] | |||

}} | }} | ||

| Line 23: | Line 24: | ||

== Hardware (Actel variant) == | == Hardware (Actel variant) == | ||

The PCB is marked "Saleae16 v4.6 By mcupro". | |||

* '''FPGA''': [https://www.actel.com/documents/PA3_DS.pdf Actel A3P125] | * '''FPGA''': [https://www.actel.com/documents/PA3_DS.pdf Actel A3P125] | ||

| Line 31: | Line 34: | ||

* '''Crystal''': 24MHz | * '''Crystal''': 24MHz | ||

== Hardware ( | == Hardware (Cyclone variant) == | ||

The PCB doesn't have any identifying markings. | |||

* '''FPGA''': [https://www.altera.com/products/fpga/cyclone-series/cyclone/support.html#Cyclone-Device-Handbook--All-Sections- Altera Cyclone EP1C3T100] | * '''FPGA''': [https://www.altera.com/products/fpga/cyclone-series/cyclone/support.html#Cyclone-Device-Handbook--All-Sections- Altera Cyclone EP1C3T100] | ||

| Line 40: | Line 45: | ||

* '''Crystal (FX2)''': 24MHz | * '''Crystal (FX2)''': 24MHz | ||

* '''Crystal (FPGA)''': 100MHz | * '''Crystal (FPGA)''': 100MHz | ||

* '''FPGA bitstream''': | * '''FPGA bitstream''': ST M25P10VP, 1Mbit SPI NOR flash ([https://cdn.datasheetspdf.com/pdf-down/2/5/P/25P10VP-STMicroelectronics.pdf datasheet]) | ||

* '''Bootstrap controller''': STCMCU 15F10, 8051 compatible | * '''Bootstrap controller''': [http://www.stcmcu.com/datasheet/stc/STC-AD-PDF/STC15.pdf STCMCU 15F10], 8051 compatible | ||

== Hardware (2018 variant) == | |||

The PCB is marked "Logic 16 Saleae". This variant also comes in a case identical to the [[Noname_XL-LOGIC16-100M]]. | |||

* '''FPGA''': Markings ground off, but pinout indicates an Altera Cyclone EP1C3T144. | |||

* '''USB interface chip''': [http://www.cypress.com/?docID=45142 Cypress CY7C68013A] | |||

* '''I²C EEPROM''': Markings ground off | |||

* '''3.3V voltage regulator''': [http://www.techcodesemi.com/cn/products_info.asp?pid=26 TD 6810] adjustable version + 150k/680k resistors pair | |||

* '''1.5V voltage regulator''': [http://www.techcodesemi.com/cn/products_info.asp?pid=26 TD 6810] adjustable version + 160k/240k resistors pair | |||

* '''Crystal (FX2)''': 24MHz | |||

* '''Crystal (FPGA)''': 32MHz | |||

* '''FPGA bitstream''': ST M25P10VP, 1Mbit SPI NOR flash ([https://cdn.datasheetspdf.com/pdf-down/2/5/P/25P10VP-STMicroelectronics.pdf datasheet]) | |||

* '''Bootstrap controller''': Not required? | |||

== Hardware (2015-01-08 variant) == | == Hardware (2015-01-08 variant) == | ||

| Line 54: | Line 73: | ||

* '''Crystal (FX2)''': 24MHz | * '''Crystal (FX2)''': 24MHz | ||

* '''Crystal (FPGA)''': Looks like 32MHz? | * '''Crystal (FPGA)''': Looks like 32MHz? | ||

* '''FPGA bitstream''': | * '''FPGA bitstream''': ST M25P10VP, 1Mbit SPI NOR flash ([https://cdn.datasheetspdf.com/pdf-down/2/5/P/25P10VP-STMicroelectronics.pdf datasheet]) | ||

* '''Bootstrap controller''': Not required? | * '''Bootstrap controller''': Not required? | ||

| Line 61: | Line 80: | ||

The PCB is marked "Saleae Logic 16 mcupro 2014.1.25". | The PCB is marked "Saleae Logic 16 mcupro 2014.1.25". | ||

The bottom two channels are not GND, but SCK (sample clock out) and HCK (half of SCK out). | |||

* '''FPGA''': Markings ground off, but pinout and JTAG (IDCODE 0x020810dd) indicate an Altera Cyclone EP1C3T100. | |||

* '''USB interface chip''': Markings sometimes ground off? Cypress CY7C68013A | |||

* '''Crystal (FX2)''': marked "DKF 24.000" | |||

* '''Crystal (FPGA)''': marked "RAK32.00" | |||

* '''FPGA bitstream''': ST M25P10VP, 1Mbit SPI NOR flash ([https://cdn.datasheetspdf.com/pdf-down/2/5/P/25P10VP-STMicroelectronics.pdf datasheet]) | |||

* '''I²C EEPROM''': None? (CY7C68013A I2C port wired to FPGA pins) | |||

* '''Bootstrap controller''': Markings ground off, pinout could indicate a [http://www.stcmcu.com/datasheet/stc/STC-AD-PDF/STC15.pdf STCMCU 15F10x] 8051-based MCU? | |||

* '''3.3V voltage regulator''': unknown switching regulator (marked "IC5CJ" ?) + 150k/680k resistors pair | |||

* '''1.5V voltage regulator''': unknown switching regulator (marked "IC5CJ" ?) + 160k/240k resistors pair | |||

* '''Channel input buffering''': none, only simple resistor (510R) + TVS diode array protection (possibly [http://www.semtech.com/images/datasheet/srv05-4.pdf Semtech SRV05]) | |||

== Photos (Actel) == | == Photos (Actel) == | ||

| Line 82: | Line 109: | ||

File:Mcupro Logic16 Variant2 top.jpg|<small>PCB with Altera Cyclone, top</small> | File:Mcupro Logic16 Variant2 top.jpg|<small>PCB with Altera Cyclone, top</small> | ||

File:IMG 0207 v1.JPG|<small>PCB with Altera Cyclone, bottom</small> | File:IMG 0207 v1.JPG|<small>PCB with Altera Cyclone, bottom</small> | ||

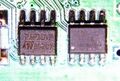

File:Mcupro Logic16 Variant2 top flash+uC.jpg|<small>PCB, top, | File:Mcupro Logic16 Variant2 top flash+uC.jpg|<small>PCB, top, 1Mbit flash and STCMCU uC</small> | ||

</gallery> | |||

== Photos (2018 variant) == | |||

<gallery> | |||

File:Mcupro-2018-case.jpg|<small>Device, top</small> | |||

File:Mcupro-2018-front.jpg|<small>PCB, top</small> | |||

File:Mcupro-2018-back.jpg|<small>PCB, bottom</small> | |||

</gallery> | </gallery> | ||

| Line 91: | Line 126: | ||

File:Mcupro-2015-1-8-top-overview.jpg|<small>PCB, top</small> | File:Mcupro-2015-1-8-top-overview.jpg|<small>PCB, top</small> | ||

File:Mcupro-2015-1-8-bottom-overview.jpg|<small>PCB, bottom</small> | File:Mcupro-2015-1-8-bottom-overview.jpg|<small>PCB, bottom</small> | ||

File:Mcupro-2015-1-8-voltage-regulators.jpg|<small>PCB, 3. | File:Mcupro-2015-1-8-voltage-regulators.jpg|<small>PCB, 3.3V and 1.5V voltage regulators</small> | ||

File:Mcupro-2015-1-8-bottom-markings-intact.jpg|<small>PCB, bottom - chip markings intact</small> | File:Mcupro-2015-1-8-bottom-markings-intact.jpg|<small>PCB, bottom - chip markings intact</small> | ||

</gallery> | </gallery> | ||

| Line 99: | Line 134: | ||

<gallery> | <gallery> | ||

File:seleae-logic16-aliexpress-clone.jpg|<small>Device, top</small> | File:seleae-logic16-aliexpress-clone.jpg|<small>Device, top</small> | ||

File:Mcupro-2014-1-25-top_ortho.jpg|<small>PCB, top detail</small> | |||

File:Mcupro-2014-1-25-bottom_ortho.jpg|<small>PCB, bottom detail</small> | |||

File:Mcupro-2014-1-25-top-overview.jpg|<small>PCB, top</small> | File:Mcupro-2014-1-25-top-overview.jpg|<small>PCB, top</small> | ||

File:Mcupro-2014-1-25-bottom-overview.jpg|<small>PCB, bottom</small> | File:Mcupro-2014-1-25-bottom-overview.jpg|<small>PCB, bottom</small> | ||

| Line 113: | Line 150: | ||

;Cyclone variant | ;Cyclone variant | ||

: This logic analyzer works with unmodified Saleae software. The PCB contains an SPI flash chip, so it only requires an upload of Cypress FX2LP firmware in order to operate. | : This logic analyzer works with unmodified Saleae software. The PCB contains an SPI flash chip, so it only requires an upload of Cypress FX2LP firmware in order to operate. | ||

;2015-01-08 | ;2015-01-08 and 2018 variants | ||

: Only requires an upload of Cypress FX2LP firmware to operate. Open-source binaries from [https://github.com/gregani/la16fw gregani] work, but must be renamed to '''saleae-logic16-fx2.fw'''. It also requires a [[libsigrok]] more recent than 2014-08-22 to work (see bug [http://sigrok.org/bugzilla/show_bug.cgi?id=680#c4 #680]). | : Only requires an upload of Cypress FX2LP firmware to operate. Open-source binaries from [https://github.com/gregani/la16fw gregani] work, but must be renamed to '''saleae-logic16-fx2.fw'''. It also requires a [[libsigrok]] more recent than 2014-08-22 to work (see bug [http://sigrok.org/bugzilla/show_bug.cgi?id=680#c4 #680]). | ||

;2014-01-25 variant | ;2014-01-25 variant | ||

Latest revision as of 13:36, 30 June 2019

| |

| Status | supported |

|---|---|

| Source code | saleae-logic16 |

| Channels | 3/6/9/16 |

| Samplerate | 100/50/32/16MHz |

| Samplerate (state) | — |

| Triggers | none (SW-only) |

| Min/max voltage | -0.9V — 6V |

| Threshold voltage | 1.5V (operates with 3.3V logic) |

| Memory | none |

| Compression | yes |

| Price range | $30 - $35 |

| Website | aliexpress.com |

The mcupro Logic16 clone is a USB-based, 16-channel logic analyzer with 100/50/32/16MHz sampling rate (at 3/6/9/16 enabled channels).

This is a clone of the Saleae Logic16.

See mcupro Logic16 clone/Info for more details (such as lsusb -v output) about the device.

Hardware (Actel variant)

The PCB is marked "Saleae16 v4.6 By mcupro".

- FPGA: Actel A3P125

- USB interface chip: Cypress CY7C68013A

- I²C EEPROM: Atmel 24C02N

- 3.3V voltage regulator: Advanced Monolithic Systems AMS1117-3.3

- 1.5V voltage regulator: Advanced Monolithic Systems AMS1117-1.5

- Crystal: 24MHz

Hardware (Cyclone variant)

The PCB doesn't have any identifying markings.

- FPGA: Altera Cyclone EP1C3T100

- USB interface chip: Cypress CY7C68013A

- I²C EEPROM: Atmel 24C02N

- 3.3V voltage regulator: Advanced Monolithic Systems AMS1117-3.3

- 1.5V voltage regulator: Advanced Monolithic Systems AMS1117-1.5

- Crystal (FX2): 24MHz

- Crystal (FPGA): 100MHz

- FPGA bitstream: ST M25P10VP, 1Mbit SPI NOR flash (datasheet)

- Bootstrap controller: STCMCU 15F10, 8051 compatible

Hardware (2018 variant)

The PCB is marked "Logic 16 Saleae". This variant also comes in a case identical to the Noname_XL-LOGIC16-100M.

- FPGA: Markings ground off, but pinout indicates an Altera Cyclone EP1C3T144.

- USB interface chip: Cypress CY7C68013A

- I²C EEPROM: Markings ground off

- 3.3V voltage regulator: TD 6810 adjustable version + 150k/680k resistors pair

- 1.5V voltage regulator: TD 6810 adjustable version + 160k/240k resistors pair

- Crystal (FX2): 24MHz

- Crystal (FPGA): 32MHz

- FPGA bitstream: ST M25P10VP, 1Mbit SPI NOR flash (datasheet)

- Bootstrap controller: Not required?

Hardware (2015-01-08 variant)

The PCB is marked "Saleae Logic 16 By MCUPro 2015-1-8". Readily identifiable by the irregular PCB traces, and switching power supplies. This comes in a different case, identical to the Noname_XL-LOGIC16-100M.

- FPGA: Markings ground off

- USB interface chip: Cypress CY7C68013A

- I²C EEPROM: Markings ground off

- 3.3V voltage regulator: TD 6810 adjustable version + 150k/680k resistors pair

- 1.5V voltage regulator: TD 6810 adjustable version + 160k/240k resistors pair

- Crystal (FX2): 24MHz

- Crystal (FPGA): Looks like 32MHz?

- FPGA bitstream: ST M25P10VP, 1Mbit SPI NOR flash (datasheet)

- Bootstrap controller: Not required?

Hardware (2014-01-25 variant)

The PCB is marked "Saleae Logic 16 mcupro 2014.1.25".

The bottom two channels are not GND, but SCK (sample clock out) and HCK (half of SCK out).

- FPGA: Markings ground off, but pinout and JTAG (IDCODE 0x020810dd) indicate an Altera Cyclone EP1C3T100.

- USB interface chip: Markings sometimes ground off? Cypress CY7C68013A

- Crystal (FX2): marked "DKF 24.000"

- Crystal (FPGA): marked "RAK32.00"

- FPGA bitstream: ST M25P10VP, 1Mbit SPI NOR flash (datasheet)

- I²C EEPROM: None? (CY7C68013A I2C port wired to FPGA pins)

- Bootstrap controller: Markings ground off, pinout could indicate a STCMCU 15F10x 8051-based MCU?

- 3.3V voltage regulator: unknown switching regulator (marked "IC5CJ" ?) + 150k/680k resistors pair

- 1.5V voltage regulator: unknown switching regulator (marked "IC5CJ" ?) + 160k/240k resistors pair

- Channel input buffering: none, only simple resistor (510R) + TVS diode array protection (possibly Semtech SRV05)

Photos (Actel)

Photos (Cyclone)

Photos (2018 variant)

Photos (2015-01-08 variant)

Photos (2014-01-25 variant)

Protocol

Firmware

- Actel variant

- This logic analyzer works with unmodified Saleae software. The Actel FPGA has on-chip flash storage, so it only requires an upload of Cypress FX2LP firmware in order to operate.

- Cyclone variant

- This logic analyzer works with unmodified Saleae software. The PCB contains an SPI flash chip, so it only requires an upload of Cypress FX2LP firmware in order to operate.

- 2015-01-08 and 2018 variants

- Only requires an upload of Cypress FX2LP firmware to operate. Open-source binaries from gregani work, but must be renamed to saleae-logic16-fx2.fw. It also requires a libsigrok more recent than 2014-08-22 to work (see bug #680).

- 2014-01-25 variant

- Seems to have the bitstream in internal flash, so it only requires an upload of Cypress FX2LP firmware in order to operate. This requires a libsigrok more recent than 2014-08-22 to work (see bug #680).

The firmware extraction steps are identical to steps for Saleae Logic16, however you only need to have saleae-logic16-fx2.fw installed.