Difference between revisions of "Main Page"

Uwe Hermann (talk | contribs) m |

Uwe Hermann (talk | contribs) m |

||

| Line 11: | Line 11: | ||

* '''Hardware support'''. Supports a wide variety of logic analyzer hardware from various vendors with different capabilities. | * '''Hardware support'''. Supports a wide variety of logic analyzer hardware from various vendors with different capabilities. | ||

* '''Cross-platform'''. Works on [[Linux]]/[[Mac OS X]]/[[Windows]]/etc. and on x86/ARM/Sparc/PowerPC/etc. | * '''Cross-platform'''. Works on [[Linux]]/[[Mac OS X]]/[[Windows]]/etc. and on x86/ARM/Sparc/PowerPC/etc. | ||

* '''Scriptable'''. Extendable with protocol decoders written in Lua or Python. | * '''Scriptable'''. Extendable with protocol decoders and analyzers written in Lua or Python. | ||

* '''Format support'''. Supports various input and output formats (raw, CSV, gnuplot, VCD, others). | * '''Format support'''. Supports various input and output formats (raw, CSV, gnuplot, [ VCD], others). | ||

== Download == | == Download == | ||

No releases have been made yet. However, development is done in a git repository. To get a copy: | No releases have been made yet. However, development is done in a [http://sigrok.git.sourceforge.net/git/gitweb.cgi?p=sigrok/sigrok;a=shortlog git repository]. To get a copy: | ||

$ '''git clone git://sigrok.git.sourceforge.net/gitroot/sigrok/sigrok''' | $ '''git clone git://sigrok.git.sourceforge.net/gitroot/sigrok/sigrok''' | ||

See [[Linux]], [[Mac OS X]], and [[Windows]] for build instructions. Binary releases and additional project information will be found on the [http://www.sourceforge.net/projects/sigrok SourceForge project page] later on. | |||

Binary releases and additional project information | |||

== Supported hardware == | == Supported hardware == | ||

<gallery> | <gallery perrow="5" > | ||

File:Cwav usbee sx.jpg|<small>'''[[CWAV USBee SX]]'''<br />(coming up)</small> | File:Cwav usbee sx.jpg|<small>'''[[CWAV USBee SX]]'''<br />(coming up)</small> | ||

File:Saleae Logic.jpg|<small>'''[[Saleae Logic]]'''<br />(supported)</small> | File:Saleae Logic.jpg|<small>'''[[Saleae Logic]]'''<br />(supported)</small> | ||

| Line 33: | Line 31: | ||

File:Zeroplus Logic Cube.jpg|<small>'''[[Zeroplus Logic Cube]]'''<br />(coming up)</small> | File:Zeroplus Logic Cube.jpg|<small>'''[[Zeroplus Logic Cube]]'''<br />(coming up)</small> | ||

</gallery> | </gallery> | ||

== Documentation == | == Documentation == | ||

| Line 50: | Line 47: | ||

== Getting in touch == | == Getting in touch == | ||

* Mailing lists: [https://lists.sourceforge.net/lists/listinfo/sigrok-devel sigrok-devel], [https://lists.sourceforge.net/lists/listinfo/sigrok-commits sigrok-commits] | * Mailing lists: [https://lists.sourceforge.net/lists/listinfo/sigrok-devel sigrok-devel], [https://lists.sourceforge.net/lists/listinfo/sigrok-commits sigrok-commits]. | ||

* IRC: '''#sigrok''' on Freenode. | * IRC: '''[irc://chat.freenode.net/sigrok #sigrok]''' on [http://www.freenode.net Freenode]. | ||

Revision as of 15:06, 18 March 2010

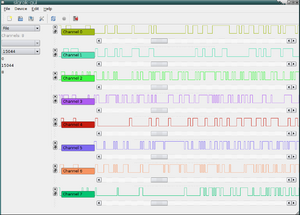

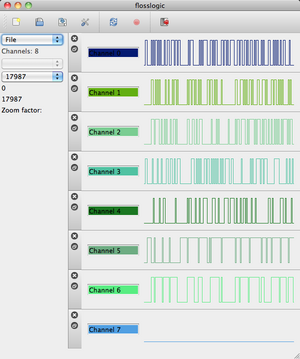

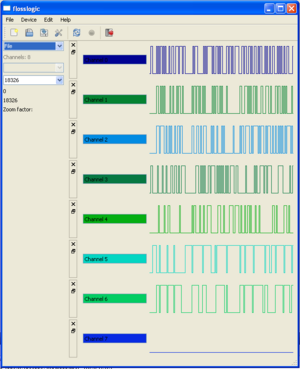

The sigrok project aims at creating a portable, cross-platform, Free/Libre/Open-Source logic analyzer software that supports various (usually USB-based) logic analyzer hardware products. The code is licensed under the terms of the GNU GPL.

Design goals

- Hardware support. Supports a wide variety of logic analyzer hardware from various vendors with different capabilities.

- Cross-platform. Works on Linux/Mac OS X/Windows/etc. and on x86/ARM/Sparc/PowerPC/etc.

- Scriptable. Extendable with protocol decoders and analyzers written in Lua or Python.

- Format support. Supports various input and output formats (raw, CSV, gnuplot, [ VCD], others).

Download

No releases have been made yet. However, development is done in a git repository. To get a copy:

$ git clone git://sigrok.git.sourceforge.net/gitroot/sigrok/sigrok

See Linux, Mac OS X, and Windows for build instructions. Binary releases and additional project information will be found on the SourceForge project page later on.

Supported hardware

CWAV USBee SX

(coming up)Saleae Logic

(supported)- Open workbench logic sniffer.jpg

Openbench Logic Sniffer

(work in progress) Braintechnology USB-LPS

(partially supported)Zeroplus Logic Cube

(coming up)

Documentation

Frontends

Getting in touch

- Mailing lists: sigrok-devel, sigrok-commits.

- IRC: #sigrok on Freenode.

IMPORTANT: Please note that (unless explicitly specified otherwise) all contents in this wiki (including text and images) are released to the CC-BY-SA 3.0. If you don't want that, please explicitly specify another free-ish license when adding pages or images to the wiki!