Difference between revisions of "Main Page"

(Moved Sigma up.) |

(Made picture of Sigma a picture of a closed Sigma.) |

||

| Line 17: | Line 17: | ||

File:Saleae Logic.jpg|<small>'''[[Saleae Logic]]'''<br />(supported)</small> | File:Saleae Logic.jpg|<small>'''[[Saleae Logic]]'''<br />(supported)</small> | ||

File:Eeelec xla esla100.jpg|<small>'''[[EE Electronics XLA ESLA100|EE Electronics XLA/ESLA100]]''' (supported)</small> | File:Eeelec xla esla100.jpg|<small>'''[[EE Electronics XLA ESLA100|EE Electronics XLA/ESLA100]]''' (supported)</small> | ||

File: | File:ASIX SIGMA.jpg|<small>'''[[ASIX SIGMA]]''' (partially supported)</small> | ||

File:Open workbench logic sniffer.jpg|<small>'''[[Openbench Logic Sniffer]]'''<br />(work in progress)</small> | File:Open workbench logic sniffer.jpg|<small>'''[[Openbench Logic Sniffer]]'''<br />(work in progress)</small> | ||

File:Zeroplus Logic Cube.jpg|<small>'''[[ZEROPLUS Logic Cube LAP-C]]''' (work in progress)</small> | File:Zeroplus Logic Cube.jpg|<small>'''[[ZEROPLUS Logic Cube LAP-C]]''' (work in progress)</small> | ||

Revision as of 17:36, 28 April 2010

|

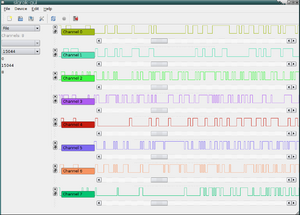

The sigrok project aims at creating a portable, cross-platform, Free/Libre/Open-Source logic analyzer software that supports various (usually USB-based) logic analyzer hardware products. The code is licensed under the terms of the GNU GPL. Design goals

Supported hardware

|

|

IMPORTANT: Please note that (unless explicitly specified otherwise) all contents in this wiki (including text and images) are released to the CC-BY-SA 3.0. If you don't want that, please explicitly specify another free-ish license when adding pages or images to the wiki!