Difference between revisions of "Protocol decoder:Nrf24l01"

| Line 68: | Line 68: | ||

SPI commands can have variable length, the CSN signal has to stay low during the whole command, and then go high after the last byte. The first byte of a command defines the type of the command, the chip always outputs its internal status register at the beginning. The following bytes are dependent on the command type, can be register values to write into the chip or payload data to send, or empty bytes that are ignored if the command only reads the output of the chip. | SPI commands can have variable length, the CSN signal has to stay low during the whole command, and then go high after the last byte. The first byte of a command defines the type of the command, the chip always outputs its internal status register at the beginning. The following bytes are dependent on the command type, can be register values to write into the chip or payload data to send, or empty bytes that are ignored if the command only reads the output of the chip. | ||

== Decoder == | |||

The <tt>nrf24l01</tt> decoder stacks on top of the SPI decoder and decodes the commands to the chip and the responses of the chip, and also issues warnings for wrong/incomplete commands. | |||

<gallery> | |||

File:NRF24L01 PD write register.png|<small>Decoded "Write Register" command.</small> | |||

File:NRF24L01 PD tx payload.png|<small>Decoded payload that is going to be transmitted.</small> | |||

File:NRF24L01 PD rx payload.png|<small>The payload on the receiver side.</small> | |||

</gallery> | |||

[[Category:Protocol decoder]] | [[Category:Protocol decoder]] | ||

[[Category:SPI]] | [[Category:SPI]] | ||

Revision as of 12:32, 24 July 2014

| |

| Name | nRF24L01(+) |

|---|---|

| Description | 2.4GHz transceiver chip |

| Status | supported |

| License | GPLv2+ |

| Source code | decoders/nrf24l01 |

| Input | spi |

| Output | nrf24l01 |

| Probes | — |

| Optional probes | — |

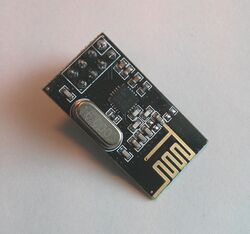

The nrf24l01 protocol decoder supports the protocol spoken by the Nordic Semiconductor nRF24L01 and nRF24L01+ 2.4GHz transceiver chips.

Hardware

Modules with these chips can be purchased fairly inexpensive from various online marketplaces. Most (all?) use the following pinout:

| Pin | Function |

|---|---|

| 1 | GND |

| 2 | VCC |

| 3 | CE |

| 4 | CSN |

| 5 | SCK |

| 6 | MOSI |

| 7 | MISO |

| 8 | IRQ |

The chip has two chip select pins, "CE" used to control the standby mode, and "CSN" used for SPI communication.

Protocol

The chip uses the standard SPI protocol and pins (CSN, SCK, MOSI, MISO), with the additional CE (used to control the RX/TX and standby modes) and IRQ (used to inform the SPI master about the completion of a packet reception/transmission) signals. If the number of available pins of the master are scare, the CE pin can be tied to VCC and the IRQ ping can be left open, instead of it polling over SPI can be used.

SPI commands can have variable length, the CSN signal has to stay low during the whole command, and then go high after the last byte. The first byte of a command defines the type of the command, the chip always outputs its internal status register at the beginning. The following bytes are dependent on the command type, can be register values to write into the chip or payload data to send, or empty bytes that are ignored if the command only reads the output of the chip.

Decoder

The nrf24l01 decoder stacks on top of the SPI decoder and decodes the commands to the chip and the responses of the chip, and also issues warnings for wrong/incomplete commands.