Difference between revisions of "CoLA"

m |

m |

||

| Line 49: | Line 49: | ||

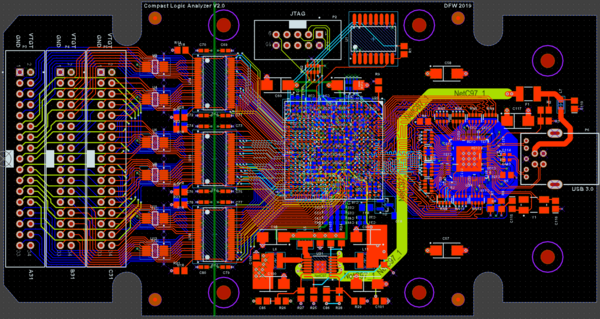

== Design == | == Design == | ||

The overall design of the CoLA has two parts: A populated PCB, and an enclosure. The reference design uses a Hammond Manufacturing 1553DTBUBKBAT semi-transparent plastic enclosure. It has minimal exposed metal parts to minimize unwanted short circuits, as the unit is meant to be used near exposed PCB's. The enclosure has a seperate part with a lid, originally meant to house a 9V style battery. This part is used in the CoLA to expose three 34-pin headers to input all signals. Minimal modification is needed to the enclosure to accomodate the PCB. | The overall design of the CoLA has two parts: A populated PCB, and an enclosure. The reference design uses a Hammond Manufacturing 1553DTBUBKBAT semi-transparent plastic enclosure. It has minimal exposed metal parts to minimize unwanted short circuits, as the unit is meant to be used near exposed PCB's. The enclosure has a seperate part with a lid, originally meant to house a 9V style battery. This part is used in the CoLA to expose three 34-pin headers to input all signals. Minimal modification is needed to the enclosure to accomodate the PCB. | ||

[[File:1553DTBUBKBAT.jpg|600px]] | |||

The single PCB holds all the electronic components that make the design work. A USB3 B-type connector is used to ruggedize the design, as it is not as fragile compared to a Micro-B or C style connector. The FTDI FT601B-Q ensures steady communication over the USB bus. The parallel bus towards the FPGA is lenght-equalized, to minimize the risk of transmission errors. | The single PCB holds all the electronic components that make the design work. A USB3 B-type connector is used to ruggedize the design, as it is not as fragile compared to a Micro-B or C style connector. The FTDI FT601B-Q ensures steady communication over the USB bus. The parallel bus towards the FPGA is lenght-equalized, to minimize the risk of transmission errors. | ||

Revision as of 19:05, 11 December 2019

| |

| Status | planned |

|---|---|

| Source code | - |

| Channels | 96/48/24 |

| Samplerate | 25MHz/50MHz/100MHz |

| Samplerate (state) | ? |

| Triggers | 32 hardware, 96 bit masked pattern |

| Min/max voltage | 1.65V - 5.5V continuously |

| Threshold voltage | ? |

| Memory | 262144 bytes |

| Compression | RLE, frame omission |

| Website | - |

Introduction

CoLA - Compact Logic Analyzer is an USB3.0 based 96ch/25MHz, 48ch/50MHz or 24ch/100MHz logic analyzer/pattern generator, with built-in hardware pattern triggers, supporting all logic levels from 1.65V to 5.5V. It uses an Intel/Altera Cyclone V FPGA for digital aquisition and FTDI FT601B for 5Gbps USB3.0 support. To limit data transfers, it uses Run Length Encoding (RLE) as well as frame omission. Its compact design and versatility, as well as future upgradability and a DIY approach makes CoLA an interesting project.

Theory

The aquisition of digital levels are done by an FPGA. The Intel/Altera Cyclone V series have sufficient speed and resources. Although versions with High Speed Serial Interfaces (HSSI's) and an embedded ARM Host Processor System (HPS) exist, a part without these is selected. The 5CEBA5F23C8 has 29.000 ALM / 77.000 LE's and 446 M10K memory blocks of resources. For now, the 150 DSP hardware multiplier modules are not used, but that can change in the future. The FPGA is also equipped with 6 PLL blocks, but only one is used.

To transfer all data to a computer, a part from FTDI is used to communicate over the USB bus. The FT601 has a 5Gbps transceiver, of which 3200Mbps can be used by the chip. The USB chip interfaces to the FPGA by means of a parallel data bus, 32 bits at 100MHz. It uses an external 30MHz crystal to generate all frequencies, and the FPGA inputs the 100MHz clock as its main clock frequency. Apart from the 32 data bits, some other arbitration signals are used.

The 96 inputs/outputs of the CoLA are equipped with logic level translators and diode clamps, to translate and protect from 1.65V to 5.5V, into the 3.3V logic levels that is used inside. The inputs are not isolated and a common ground is used. Data direction can be changed on a per-byte basis.

Inside the FPGA, the logic analyzer parts is divided into three major parts. First, the 96 inputs are routed through a connection matrix-like multiplexer, so every physical input can be routed freely onto every one of the 96 possible input channels. Secondly, the input channels are fed though a framer/packetizer, which outputs frames with a proper preamble and data compression. These frames are stored in a data buffer, ready to transmit. The third and final part is the communication interface with the FT601B chip, that sends data from the buffer and receives configuration information.

Data transmission

Data transmission coming from the CoLA are formatted in 4 byte (32 bit) frames, each of which consists of a 1 byte preamble and a 3 byte data portion:

| Preamble | Data |

|---|---|

| 0x82 | bits 95 - 72 |

| 0x81 | bits 71 - 48 |

| 0x80 | bits 47 - 24 |

| 0x00 - 0x7F | bits 23 - 0 |

Data compression is accomplished in two ways: If nothing changes in input channel bits 95 - 72, the 0x82 frame is omitted completely. Likewise, if channel inputs 71 - 48 or 47 - 24 are unchanged, frame 0x81 and 0x80 respectively are omitted. If nothing changes in inputs 23 - 0, the preamble is increased by 1. This is called the RLE counter. If it finally reaches 0x7F, the frame is sent, and the preamble is reset to 0x00. Using this scheme, data compression can be done in realtime, and with an empty input, a 252:1 ratio can be accomplished. Of course, if the input channel data does change, the frame sent. The hardware WILL send lower preamble frames if a higher one MUST be transmitted. Also, when a USB transmission is started, it triggers a complete preamble set of 0x82, 0x81, 0x80 and 0x00-0x7F, depending on the RLE counter. This is done to provide regular reference points, similar to keyframes in a compressed video stream.

Design

The overall design of the CoLA has two parts: A populated PCB, and an enclosure. The reference design uses a Hammond Manufacturing 1553DTBUBKBAT semi-transparent plastic enclosure. It has minimal exposed metal parts to minimize unwanted short circuits, as the unit is meant to be used near exposed PCB's. The enclosure has a seperate part with a lid, originally meant to house a 9V style battery. This part is used in the CoLA to expose three 34-pin headers to input all signals. Minimal modification is needed to the enclosure to accomodate the PCB.

The single PCB holds all the electronic components that make the design work. A USB3 B-type connector is used to ruggedize the design, as it is not as fragile compared to a Micro-B or C style connector. The FTDI FT601B-Q ensures steady communication over the USB bus. The parallel bus towards the FPGA is lenght-equalized, to minimize the risk of transmission errors.

Apart from communication, the USB connector also provides supply power to the logic analyzer. The 5V input voltage is converted to a 1.1V core, 2.5V auxilary and 3.3V I/O voltage with a Linear Technology LTC3569. This is a triple buck converter, capable of outputting 1 x 1.2A and 2 x 600mA at a high efficiency of over 90%. The 1.1V core voltage is connected to the 1.2A channel, as it is expected to draw the most current.

The 5CEBA5F23C8N is a 484 ball BGA style chip, with a 1mm pitch. As far as BGA's are DIY friendly at all, this is the most DIY friendly version of any of the packages that the Cyclone V FPGA comes in. As the fanout of this part is not that easy, a 6 layer PCB must be used to route all of the signals from and to the FPGA. Decoupling capacitors are best placed close to ther power pins, so many of them are placed at the opposite PCB side of the FPGA. To store the FPGA configuration image, a EPCQ64A flash is used in Active Serial mode.

For level conversion, a large number of signals needs to be supported. Because the CoLA can also act as a digital pattern generator, data direction signals are also used to drive the six 74LVC16T245DGGR level translators. These are directly connected to the input channels. Input protection is only done by diode clamping, by using twelve SP3003-08ATG 8 channel TVS protection devices. All of the digital channels are present on three 34-pin header connectors, each of which is also equipped with a supply and ground.

Schematics

The schematics of this design can be divided into 5 major blocks. The Input Connector with its Diode Protection devices, the Voltage level Translators, the FPGA as the heart of the device, the USB interface and the Power Supply. All IC's are sufficiently provided with decoupling capacitors, with 2 different values to cover a wider frequency range. The analog PLL voltages of the FPGA are additionally decoupled by means of a ferrite bead. The power supplies have a high switching frequency, but large bulk capacitors of 100uF are provided to handle any kind of current spikes.

File:CoLA Schematics.zip Password: sigrok