Difference between revisions of "Saanlima Pipistrello OLS"

(Created page with "{{Infobox logic analyzer | image = 180px | name = Saanlima Pipistrello OLS | status = in progress | sour...") |

Uwe Hermann (talk | contribs) |

||

| (5 intermediate revisions by 2 users not shown) | |||

| Line 2: | Line 2: | ||

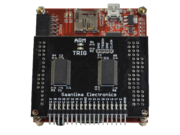

| image = [[File:Saanlima Pipistrello-OLS.png|180px]] | | image = [[File:Saanlima Pipistrello-OLS.png|180px]] | ||

| name = Saanlima Pipistrello OLS | | name = Saanlima Pipistrello OLS | ||

| status = | | status = supported | ||

| source_code_dir = pipistrello-ols | | source_code_dir = pipistrello-ols | ||

| channels = 32 | | channels = 32 | ||

| Line 12: | Line 12: | ||

| memory = 64MiB | | memory = 64MiB | ||

| compression = yes | | compression = yes | ||

| website = [http://pipistrello.saanlima.com/index.php?title=Welcome_to_Pipistrello | | website = [http://pipistrello.saanlima.com/index.php?title=Welcome_to_Pipistrello saanlima.com] | ||

}} | }} | ||

The '''Saanlima Pipistrello''' is an FPGA development board with many on-board peripherals and pin headers compatible with the [http://www.gadgetfactory.net/papilio/ Papilio] series of boards. It has USB connectivity to a host PC, and, by adding the [http://saanlima.com/store/index.php?route=product/product&product_id=55 Saanlima buffer wing], can be used as a replacement for the [[Openbench Logic Sniffer]] (OLS). | The '''Saanlima Pipistrello''' is an FPGA development board with many on-board peripherals and pin headers compatible with the [http://www.gadgetfactory.net/papilio/ Papilio] series of boards. It has USB connectivity to a host PC, and, by adding the [http://saanlima.com/store/index.php?route=product/product&product_id=55 Saanlima buffer wing], can be used as a replacement for the [[Openbench Logic Sniffer]] (OLS). | ||

The FPGA firmware for the OLS has been ported for the Pipistrello, and can thus use the full 64MiB memory to store samples. It also has triggers on rising/falling edges as an extra feature. | The FPGA firmware for the OLS has been ported for the Pipistrello, and can thus use the full 64MiB memory to store samples. It also has triggers on rising/falling edges as an extra feature. | ||

See [[Saanlima Pipistrello OLS/Info]] for more details (such as '''lsusb - | All design source for the Pipistrello, including schematics and Eagle board files, are available under the [https://creativecommons.org/licenses/by-sa/4.0/ CC-BY-SA 4.0] license. | ||

See [[Saanlima Pipistrello OLS/Info]] for more details (such as '''lsusb -v''' output) about the device. | |||

== Hardware == | == Hardware == | ||

'''Pipistrello 2.0 board''' | |||

* [http://www.xilinx.com/support/documentation/data_sheets/ds160.pdf Xilinx Spartan-6 LX45] FPGA | |||

* [http://www.micron.com/-/media/documents/products/data%20sheet/nor%20flash/serial%20nor/n25q/n25q_128mb_3v_65nm.pdf Micron N25Q128A13ESE40G] 16MiB Flash | |||

* [http://www.micron.com/-/media/documents/products/data%20sheet/dram/mobile%20dram/low-power%20dram/lpddr/60-series/t67m_512mb_mobile_lpddr_sdram.pdf Micron MT46H32M16LFBF-5] 64MiB DRAM | |||

* [http://www.ftdichip.com/Support/Documents/DataSheets/ICs/DS_FT2232H.pdf FTDI FT2232H] USB interface | |||

'''Buffer wing''' | |||

* 2 x [http://www.nxp.com/documents/data_sheet/74LVC_LVCH16245A.pdf NXP 74LVC16245A] 16-bit 5V-tolerant transceivers | |||

== Protocol == | == Protocol == | ||

The protocol used is the same as the [[Openbench Logic Sniffer#Protocol|OLS protocol]], with the addition of commands for edge triggers. See the source code for details. | The protocol used is the same as the [[Openbench Logic Sniffer#Protocol|OLS protocol]], with the addition of commands for edge triggers. See the source code for details. | ||

The Pipistrello needs to be manually flashed with a FPGA bitstream to work with sigrok. These bitstreams can be downloaded from [http://pipistrello.saanlima.com/index.php?title=Pipistrello_as_Logic_Analyzer the Pipistrello wiki] and the source code is available (see [https://sigrok.org/bugzilla/show_bug.cgi?id=1021 bug #1021] about possible automation for for this). | |||

'''Important''': The Pipistrello OLS driver [http://forum.gadgetfactory.net/index.php?/topic/1864-fpga-as-usb-pia/&do=findComment&comment=18847 only supports using the FIFO mode bitstream] and the FTDI chip has been switched to FIFO mode. If using the UART mode bitstream, use the [[Openbench Logic Sniffer]] driver '''instead''' (see [https://sigrok.org/bugzilla/show_bug.cgi?id=1020 bug #1020] about automated detection for this). | |||

== Photos == | == Photos == | ||

<gallery> | <gallery> | ||

File:Saanlima Pipistrello.jpg|<small>Pipistrello board</small> | File:Saanlima Pipistrello.jpg|<small>Pipistrello board</small> | ||

| Line 33: | Line 49: | ||

</gallery> | </gallery> | ||

== Resources == | |||

* [http://pipistrello.saanlima.com/index.php?title=Welcome_to_Pipistrello Saanlima Pipistrello] | |||

* [http://saanlima.com/forum/viewforum.php?f=3&sid=d8f2eaf446327493dd36a7132da1cc52 Pipistrello support forum] | |||

[[Category:Device]] | [[Category:Device]] | ||

[[Category:Logic analyzer]] | [[Category:Logic analyzer]] | ||

[[Category: | [[Category:Supported]] | ||

[[Category:Sump protocol]] | |||

[[Category:Open source hardware]] | |||

Latest revision as of 15:36, 2 October 2018

| |

| Status | supported |

|---|---|

| Source code | pipistrello-ols |

| Channels | 32 |

| Samplerate | 0-100MHz |

| Samplerate (state) | — |

| Triggers | value, rising/falling edge |

| Min/max voltage | 0V — 5V |

| Memory | 64MiB |

| Compression | yes |

| Website | saanlima.com |

The Saanlima Pipistrello is an FPGA development board with many on-board peripherals and pin headers compatible with the Papilio series of boards. It has USB connectivity to a host PC, and, by adding the Saanlima buffer wing, can be used as a replacement for the Openbench Logic Sniffer (OLS).

The FPGA firmware for the OLS has been ported for the Pipistrello, and can thus use the full 64MiB memory to store samples. It also has triggers on rising/falling edges as an extra feature.

All design source for the Pipistrello, including schematics and Eagle board files, are available under the CC-BY-SA 4.0 license.

See Saanlima Pipistrello OLS/Info for more details (such as lsusb -v output) about the device.

Hardware

Pipistrello 2.0 board

- Xilinx Spartan-6 LX45 FPGA

- Micron N25Q128A13ESE40G 16MiB Flash

- Micron MT46H32M16LFBF-5 64MiB DRAM

- FTDI FT2232H USB interface

Buffer wing

- 2 x NXP 74LVC16245A 16-bit 5V-tolerant transceivers

Protocol

The protocol used is the same as the OLS protocol, with the addition of commands for edge triggers. See the source code for details.

The Pipistrello needs to be manually flashed with a FPGA bitstream to work with sigrok. These bitstreams can be downloaded from the Pipistrello wiki and the source code is available (see bug #1021 about possible automation for for this).

Important: The Pipistrello OLS driver only supports using the FIFO mode bitstream and the FTDI chip has been switched to FIFO mode. If using the UART mode bitstream, use the Openbench Logic Sniffer driver instead (see bug #1020 about automated detection for this).