Difference between revisions of "Mcupro Logic16 clone"

Jump to navigation

Jump to search

Whitequark (talk | contribs) (Created page with "{{DISPLAYTITLE:mcupro Saleae16}} {{Infobox logic analyzer | image = File:USB-Logic-Analyzer-100M-max-sample-rate-16Channels-10B-samples-MCU-ARM-FPGA-debug-tool.j...") |

Whitequark (talk | contribs) m |

||

| Line 26: | Line 26: | ||

* '''FPGA''': [https://www.actel.com/documents/PA3_DS.pdf Actel A3P125] | * '''FPGA''': [https://www.actel.com/documents/PA3_DS.pdf Actel A3P125] | ||

* '''USB interface chip''': [www.cypress.com/?docID=45142 Cypress CY7C68013A] | * '''USB interface chip''': [http://www.cypress.com/?docID=45142 Cypress CY7C68013A] | ||

* '''I2C EEPROM''': [http://www.atmel.com/Images/doc3256.pdf Atmel 24C02N] | * '''I2C EEPROM''': [http://www.atmel.com/Images/doc3256.pdf Atmel 24C02N] | ||

* '''3.3V voltage regulator''': [http://ams-semitech.com/attachments/File/AMS1117_20120314.pdf Advanced Monolithic Systems AMS1117-3.3] | * '''3.3V voltage regulator''': [http://ams-semitech.com/attachments/File/AMS1117_20120314.pdf Advanced Monolithic Systems AMS1117-3.3] | ||

Revision as of 18:27, 22 August 2014

| File:USB-Logic-Analyzer-100M-max-sample-rate-16Channels-10B-samples-MCU-ARM-FPGA-debug-tool.jpg | |

| Status | planned |

|---|---|

| Source code | saleae-logic16 |

| Channels | 3/6/9/16 |

| Samplerate | 100/50/32/16MHz |

| Samplerate (state) | — |

| Triggers | none (SW-only) |

| Min/max voltage | -0.9V — 6V |

| Threshold voltage |

configurable: for 1.8V to 3.6V systems: VIH=1.4V, VIL=0.7V for 5V systems: VIH=3.6V, VIL=1.4V |

| Memory | none |

| Compression | yes |

| Website | [1] |

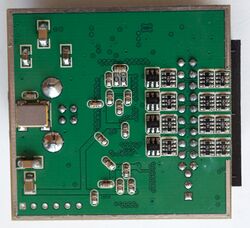

The mcupro Saleae16 is a USB-based, 16-channel logic analyzer with 100/50/32/16MHz sampling rate (at 3/6/9/16 enabled channels).

This is a clone of the Saleae Logic16.

See Mcupro Saleae16/Info for more details (such as lsusb -vvv output) about the device.

Hardware

- FPGA: Actel A3P125

- USB interface chip: Cypress CY7C68013A

- I2C EEPROM: Atmel 24C02N

- 3.3V voltage regulator: Advanced Monolithic Systems AMS1117-3.3

- 1.2V voltage regulator: Advanced Monolithic Systems AMS1117-1.5

- Crystal: 24.000MHz

Operation

This logic analyzer works with unmodified Saleae software. The Actel FPGA has on-chip flash storage, so it appears that it only requires an upload of Cypress FX2LP firmware in order to operate.