Saanlima Pipistrello OLS

| |

| Status | in progress |

|---|---|

| Source code | pipistrello-ols |

| Channels | 32 |

| Samplerate | 0-100MHz |

| Samplerate (state) | — |

| Triggers | value, rising/falling edge |

| Min/max voltage | 0V — 5V |

| Memory | 64MiB |

| Compression | yes |

| Website | pipistrello.saanlima.com |

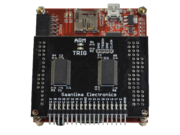

The Saanlima Pipistrello is an FPGA development board with many on-board peripherals and pin headers compatible with the Papilio series of boards. It has USB connectivity to a host PC, and, by adding the Saanlima buffer wing, can be used as a replacement for the Openbench Logic Sniffer (OLS).

The FPGA firmware for the OLS has been ported for the Pipistrello, and can thus use the full 64MiB memory to store samples. It also has triggers on rising/falling edges as an extra feature.

All design source for the Pipistrello, including schematics and Eagle board files, are available under the CC-BY-SA 4.0 license.

See Saanlima Pipistrello OLS/Info for more details (such as lsusb -vvv output) about the device.

Hardware

Protocol

The protocol used is the same as the OLS protocol, with the addition of commands for edge triggers. See the source code for details.