Difference between revisions of "Main Page"

Jump to navigation

Jump to search

| Line 29: | Line 29: | ||

<td style="vertical-align:top"> | <td style="vertical-align:top"> | ||

== | == Development == | ||

* [[TODO]] | |||

* [[Status]] | * [[Status]] | ||

* [[Design Ideas]] | * [[Design Ideas]] | ||

| Line 36: | Line 37: | ||

* [[Hardware plugin API]] | * [[Hardware plugin API]] | ||

* [[Output API]] | * [[Output API]] | ||

</td><td style="vertical-align:top"> | </td><td style="vertical-align:top"> | ||

== | == Documentation == | ||

* [[Command-line]] | * [[Command-line]] | ||

| Line 53: | Line 52: | ||

* IRC: '''[irc://chat.freenode.net/sigrok #sigrok]''' on [http://www.freenode.net Freenode]. | * IRC: '''[irc://chat.freenode.net/sigrok #sigrok]''' on [http://www.freenode.net Freenode]. | ||

* identi.ca: [http://www.identi.ca/group/sigrok sigrok group] | * identi.ca: [http://www.identi.ca/group/sigrok sigrok group] | ||

* [[Press]] | |||

</td> | </td> | ||

Revision as of 18:43, 25 March 2010

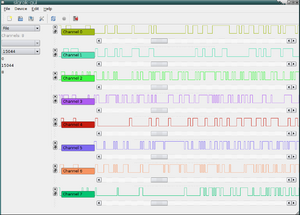

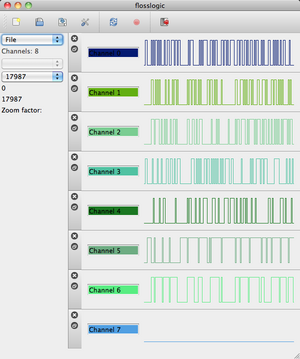

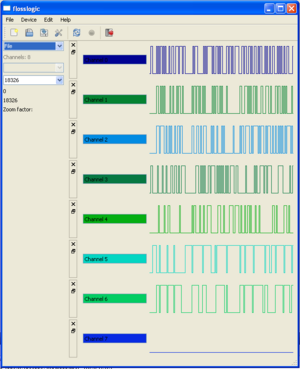

The sigrok project aims at creating a portable, cross-platform, Free/Libre/Open-Source logic analyzer software that supports various (usually USB-based) logic analyzer hardware products. The code is licensed under the terms of the GNU GPL.

Design goals

- Hardware support. Supports a wide variety of logic analyzer hardware from various vendors with different capabilities.

- Cross-platform. Works on Linux/Mac OS X/Windows/etc. and on x86/ARM/Sparc/PowerPC/etc.

- Scriptable. Extendable with protocol decoders and analyzers written in Lua or Python.

- Format support. Supports various input and output formats (raw, CSV, gnuplot, VCD, others).

Supported hardware

Saleae Logic

(supported)- Open workbench logic sniffer.jpg

Openbench Logic Sniffer

(work in progress) CWAV USBee SX

(coming up)Braintechnology USB-LPS

(planned)Zeroplus Logic Cube

(planned)- Buspirate v3.jpg

Buspirate

(planned)

Development |

Documentation |

Getting in touch

|

IMPORTANT: Please note that (unless explicitly specified otherwise) all contents in this wiki (including text and images) are released to the CC-BY-SA 3.0. If you don't want that, please explicitly specify another free-ish license when adding pages or images to the wiki!