HSA Logic

Jump to navigation

Jump to search

The printable version is no longer supported and may have rendering errors. Please update your browser bookmarks and please use the default browser print function instead.

| |

| Status | planned |

|---|---|

| Source code | hardware/hsa-tple |

| Channels | 8 (24 planned) |

| Samplerate | 6.25 MHz |

| Samplerate (state) | ? |

| Triggers | none (SW-only) |

| Min/max voltage | 3.3V; 5.0V |

| Threshold voltage | ? |

| Memory | 1 MB (245K*16), 262144 samples |

| Compression | RLE |

| Website | trac, project page, hhwiki |

The HSA Logic is a USB-based, 8-channel logic analyzer with 6.25 MHz sampling rate. It is an open-hardware / open-source design. Both hardware and software have been developed at Hochschule Augsburg so far. Everything started with this bachelor thesis in 2010. It was continued in 2013/14 as semester project.

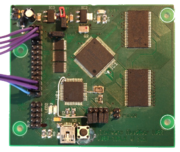

Hardware

- CPLD: Altera Max II EPM240 with 240 logic elements

- microcontroller: Atmel ATmega32u4 (programmed in C)

- 2x RAM organised as 256K*16

- I/O drivers supporting 5V and 3V as input voltage

Photos

Firmware

CPLD Firmware: written in VHDL, microcontroller Firmware: written in C (using LUFA) TODO.

Protocol

For the sake of simplicity all commands and status messages have been implemented as simple ASCII tokens (single characters).

Commands

| Command | Description |

|---|---|

| 'g' | = go, start sampling |

| 's' | = stop sampling |

| 'r' | = reset |

| 'd' | = dump data (binary) |

| 'D' | = dump data (ASCII encoded) |

| 'i' | = identify |

| 'S' | = get status |

Status messages

| Command | Description |

|---|---|

| 'r' | = measurement is running |

| 's' | = measurement stopped/ no measurement |

| 'f' | = memory is full |

Data format

The samples are blocks of 32 bit: 8 bit data, 16 bit timestamp, 8 bit status. These can be read via the dump command. The analyzer only stores new samples if any logic level changes.

Resources

TODO.