Difference between revisions of "Dangerous Prototypes Buspirate"

Jump to navigation

Jump to search

Uwe Hermann (talk | contribs) m (→Photos) |

Uwe Hermann (talk | contribs) (Use infobox, fill out a few other sections.) |

||

| Line 1: | Line 1: | ||

[[File:Buspirate | {{Infobox logic analyzer | ||

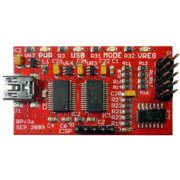

| image = [[File:Buspirate v3.png|180px]] | |||

| name = Dangerous Prototypes Buspirate | |||

| status = supported | |||

| source_code_dir = openbench-logic-sniffer | |||

| channels = 5 | |||

| samplerate = 1MHz | |||

| samplerate_state = — | |||

| triggers = ? | |||

| voltages = ? | |||

| memory = 4096 samples | |||

| compression = none | |||

| website = [http://dangerousprototypes.com/2009/11/03/bus-pirate-logic-analyzer-mode/ dangerousprototypes.com] | |||

}} | |||

The | The '''Dangerous Prototypes Buspirate''' supports a logic analyzer mode and can thus be used for sample captures, however only at low speeds. To quote from the announcement: ''The Bus Pirate can’t store a lot of samples, it can’t feed live samples very fast, and speeds are in the kHz range''. | ||

See [[Buspirate/Info]] for more details (such as '''lsusb -vvv''' output) about the device. | See [[Buspirate/Info]] for more details (such as '''lsusb -vvv''' output) about the device. | ||

| Line 8: | Line 20: | ||

== Hardware == | == Hardware == | ||

* Microchip PIC24FJ64GA | |||

* FTDI FT232RL | |||

* NXP 74HC4066D | |||

== Photos == | == Photos == | ||

| Line 22: | Line 36: | ||

== Protocol == | == Protocol == | ||

The buspirate (in logic analyzer mode) uses a simplified version of the [[Openbench_Logic_Sniffer#Protocol|"extended SUMP" protocol]]. | |||

== Resources == | == Resources == | ||

* [http://dangerousprototypes.com/docs/Bus_Pirate Bus Pirate] (main wiki page) | |||

[[Category:Device]] | [[Category:Device]] | ||

[[Category:Logic analyzer]] | [[Category:Logic analyzer]] | ||

[[Category:In progress]] | [[Category:In progress]] | ||

Revision as of 22:48, 26 April 2013

| |

| Status | supported |

|---|---|

| Source code | openbench-logic-sniffer |

| Channels | 5 |

| Samplerate | 1MHz |

| Samplerate (state) | — |

| Triggers | ? |

| Min/max voltage | ? |

| Memory | 4096 samples |

| Compression | none |

| Website | dangerousprototypes.com |

The Dangerous Prototypes Buspirate supports a logic analyzer mode and can thus be used for sample captures, however only at low speeds. To quote from the announcement: The Bus Pirate can’t store a lot of samples, it can’t feed live samples very fast, and speeds are in the kHz range.

See Buspirate/Info for more details (such as lsusb -vvv output) about the device.

Hardware

- Microchip PIC24FJ64GA

- FTDI FT232RL

- NXP 74HC4066D

Photos

Protocol

The buspirate (in logic analyzer mode) uses a simplified version of the "extended SUMP" protocol.

Resources

- Bus Pirate (main wiki page)