Difference between revisions of "Braintechnology USB-LPS"

Jump to navigation

Jump to search

Uwe Hermann (talk | contribs) (Start documenting the USB-LPS protocol.) |

Uwe Hermann (talk | contribs) m |

||

| Line 23: | Line 23: | ||

=== Starting a sampling run === | === Starting a sampling run === | ||

The host seems to send: 0x00 0x01 0x00 0x00 0x00 | |||

=== Stopping a sampling run === | |||

The host seems to send: 0x00 0x00 0x00 0x00 0x00 | |||

=== Sample rates === | === Sample rates === | ||

Sampling with 8 probes: | <table><tr valign="top"><td> | ||

'''Sampling with 8 probes:''' | |||

{| border="0" style="font-size: smaller" | {| border="0" style="font-size: smaller" | ||

| Line 33: | Line 39: | ||

!Samplerate | !Samplerate | ||

!Divider | !Divider | ||

!Other byte | |||

|- bgcolor="#eeeeee" | |- bgcolor="#eeeeee" | ||

| 24 MHz | | 24 MHz | ||

| 0x01 | | 0x01 | ||

| 0xee | |||

|- bgcolor="#dddddd" | |- bgcolor="#dddddd" | ||

| 16 MHz | | 16 MHz | ||

| 0x02 | | 0x02 | ||

| 0xee | |||

|- bgcolor="#eeeeee" | |||

| 15 MHz | |||

| 0x01 | |||

| 0xae | |||

|- bgcolor="#dddddd" | |||

| 12 MHz | |||

| 0x03 | |||

| 0xee | |||

|- bgcolor="#eeeeee" | |||

| 10 MHz | |||

| 0x02 | |||

| 0xae | |||

|- bgcolor="#dddddd" | |||

| 8 MHz | |||

| 0x05 | |||

| 0xee | |||

|- bgcolor="#eeeeee" | |||

| 6 MHz | |||

| 0x07 | |||

| 0xee | |||

|- bgcolor="#dddddd" | |||

| 5 MHz | |||

| 0x05 | |||

| 0xae | |||

|- bgcolor="#eeeeee" | |||

| 4 MHz | |||

| 0x0b | |||

| 0xee | |||

|- bgcolor="#dddddd" | |||

| 3 MHz | |||

| 0x0f | |||

| 0xae | |||

|- bgcolor="#eeeeee" | |||

| 2.5 MHz | |||

| 0x0b | |||

| 0xae | |||

|- bgcolor="#dddddd" | |||

| 2 MHz | |||

| 0x17 | |||

| 0xee | |||

|- bgcolor="#eeeeee" | |||

| 1.5 MHz | |||

| 0x1f | |||

| 0xae | |||

|- bgcolor="#dddddd" | |||

| 1 MHz | |||

| 0x2f | |||

| 0xee | |||

|- bgcolor="#eeeeee" | |- bgcolor="#eeeeee" | ||

| | | 800 kHz | ||

| | | 0x1f | ||

| 0xee | |||

|- bgcolor="#dddddd" | |||

| 750 kHz | |||

| 0x3f | |||

| 0xee | |||

|- bgcolor="#eeeeee" | |||

| 600 kHz | |||

| 0x4f | |||

| 0xee | |||

|- bgcolor="#dddddd" | |||

| 500 kHz | |||

| 0x5f | |||

| 0xee | |||

|- bgcolor="#eeeeee" | |||

| 400 kHz | |||

| 0x77 | |||

| 0xee | |||

|- bgcolor="#dddddd" | |||

| 300 kHz | |||

| 0x9f | |||

| 0xee | |||

|- bgcolor="#eeeeee" | |||

| 250 kHz | |||

| 0xbf | |||

| 0xee | |||

|- bgcolor="#dddddd" | |||

| 200 kHz | |||

| 0xef | |||

| 0xee | |||

|- bgcolor="#eeeeee" | |||

| 150 kHz | |||

| 0xc7 | |||

| 0xae | |||

|- bgcolor="#dddddd" | |||

| 120 kHz | |||

| 0xf9 | |||

| 0xae | |||

|} | |} | ||

Sampling with 16 probes: | </td><td> | ||

'''Sampling with 16 probes:''' | |||

{| border="0" style="font-size: smaller" | {| border="0" style="font-size: smaller" | ||

| Line 80: | Line 176: | ||

| ... | | ... | ||

|} | |} | ||

</td></tr></table> | |||

=== Sample format === | === Sample format === | ||

TODO. | TODO. | ||

=== Triggers === | |||

Not relevant to the protocol, happens purely in software. | |||

Revision as of 03:23, 5 January 2012

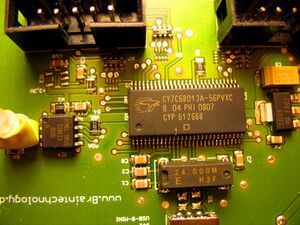

The Braintechnology USB-LPS is a Cypress FX2 based 16-channel, 24MHz, USB-based logic analyzer and signal/pattern generator.

See Braintechnology USB-LPS/Info for some more details (such as lsusb -vvv output) on the device.

Components

- Cypress CY7C68013A-56PVXC (FX2)

- Atmel ATTiny13-20SU

- LD33 (3.3V voltage regulator)

- 24MHz crystal

Protocol

Firmware upload

The FX2 firmware (3072 bytes in size) is uploaded before every sampling run. Certain bytes in the firmware differ depending on the selected sampling rate.

Starting a sampling run

The host seems to send: 0x00 0x01 0x00 0x00 0x00

Stopping a sampling run

The host seems to send: 0x00 0x00 0x00 0x00 0x00

Sample rates

|

Sampling with 8 probes:

|

Sampling with 16 probes:

|

Sample format

TODO.

Triggers

Not relevant to the protocol, happens purely in software.